CPLD內(nèi)部

CPLD內(nèi)部

相關(guān)文章 : 0篇

瀏覽 : 次

內(nèi)部自復(fù)位信號(hào)是器件上電后僅產(chǎn)生一次的信號(hào),之后一直保持無(wú)效至器件掉電。這種一次性信號(hào),產(chǎn)生它的數(shù)字電路自身需要一個(gè)初始的確定狀態(tài),并且需要上電后就處于該種狀態(tài);對(duì)于FPGA來(lái)說(shuō),其內(nèi)部寄存器在上電后的狀態(tài)是不確定的,即無(wú)法預(yù)期的,因此利用寄存器的狀態(tài)來(lái)產(chǎn)生復(fù)位信號(hào),不是那么可靠;但我們可以考慮FPGA的其他資源,一般FPGA內(nèi)部都有RAM資源,這些RAM都可以被配置數(shù)據(jù)初始化的,也就是說(shuō)當(dāng)FPGA上電配置完成后,被初始化的RAM的數(shù)據(jù)內(nèi)容是確定的。利用這個(gè)特點(diǎn),我們就可以設(shè)計(jì)可靠的內(nèi)部自復(fù)位信號(hào)。

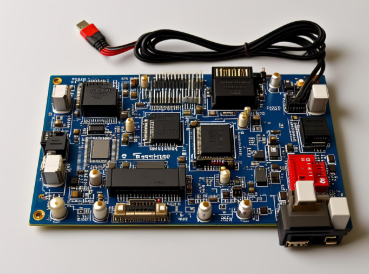

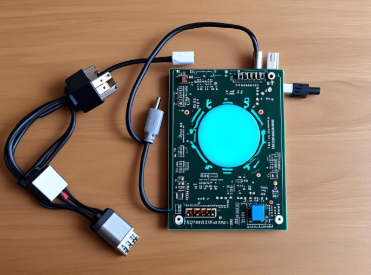

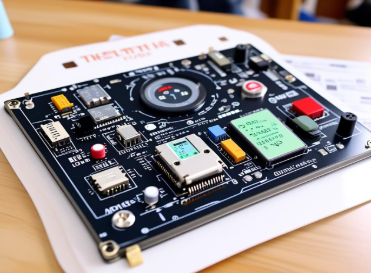

推薦產(chǎn)品

列表欄目

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)