cpld和fpga的區別:包括架構、資源規模、設計流程以及應用領域

29

29

拍明芯城

拍明芯城

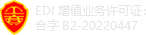

摘要:CPLD(Complex Programmable Logic Device)和FPGA(Field-Programmable Gate Array)是現代電子設備中常用的可編程邏輯器件。本文將從四個方面詳細闡述CPLD和FPGA的區別,包括架構、資源規模、設計流程以及應用領域。通過對比分析,讀者可以更好地理解這兩種器件的特點和適用場景。

一、架構

CPLD采用與門陣列(AND-OR Array)作為其主要邏輯單元,通過配置內部開關網絡實現不同功能的組合。而FPGA則使用查找表(Look-Up Table, LUT)作為基本邏輯單元,并且具有更靈活的內部連接結構。這種差異導致了CPLD在小規模應用中具有較高的性能優勢,而FPGA在大規模復雜系統中更加靈活。

此外,在資源利用率上,由于CPLD采取固定結構布局,其資源利用率相對較低;而FPGA由于可編程性強,在資源利用率上具有較高優勢。

二、資源規模

CPLD通常擁有幾千到幾萬個可編程門以及數百到數千個觸發器,適用于小規模邏輯設計。而FPGA則具有更大的資源規模,通常擁有數十萬到數百萬個可編程門以及上千到上萬個觸發器,可以滿足復雜系統的設計需求。

此外,CPLD和FPGA在存儲器資源方面也存在差異。CPLD通常只包含少量的片內存儲器(如寄存器),而FPGA則提供了更多且更靈活的存儲單元(如塊RAM、分布式RAM等),可以滿足不同應用場景對數據存儲與處理的需求。

三、設計流程

CPLD和FPGA在設計流程上也存在一定差異。對于CPLD來說,由于其較小規模和固定結構特點,在設計過程中往往采用自頂向下(Top-Down)或者類似硬件描述語言(HDL)進行高層次抽象后再進行細化實現。

而對于FPGA來說,由于其較大規模和靈活性強特點,在設計過程中往往需要充分考慮時序約束、布局布線等因素,并且可能需要進行多次迭代優化才能達到理想效果。因此,在整個設計流程中需要注重綜合、布局布線以及時序分析等環節。

四、應用領域

CPLD和FPGA在應用領域上也有一定差異。由于CPLD具有較高的性能優勢和低功耗特點,常被應用于小規模邏輯控制、時序處理以及接口轉換等場景。例如,CPLD可以廣泛應用于數字電路設計中的狀態機實現、數據選擇與分配以及信號處理等方面。

而FPGA則由于其資源規模大且靈活性強,適合用于復雜系統的設計與開發。例如,在通信領域中,FPGA可被廣泛應用于協議轉換器、高速數據傳輸接口(如PCIe)實現以及圖像/視頻處理等方面。

五、總結

本文從架構、資源規模、設計流程和應用領域四個方面詳細闡述了CPLD和FPGA的區別。通過對比分析我們可以看出,CPLD在小規模邏輯控制場景下具有較高性能優勢;而FPGA則更加靈活且適合大規模復雜系統的設計與開發。根據不同需求選擇合適的器件將有助于提高設計效率和性能。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)