模擬IP自動集成,調諧到晶圓廠節點

59

59

拍明芯城

拍明芯城

過渡到更小的節點是模擬設計的主要絆腳石。

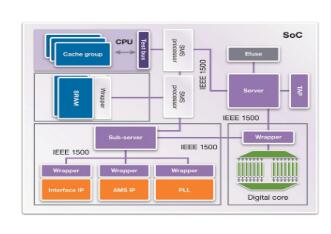

具有異構電壓域的片上系統 (SoC) 設計正越來越多地從定制模擬 IP 轉向自動化實現,因此設計工程師不必擔心手動模擬定制導致的進度延誤。它還為芯片設計人員節省了幾個月的設計過程,同時使模擬電路不易受到片上環境的影響。

請務必注意,自動生成的模擬 IP 并不等同于現成的模擬 IP。相反,模擬IP發生器將先前生成的定制設計模塊引入設計流程,并使用專用工具在數小時內定制合適的IP。反過來,這又節省了大量的集成時間和精力。

其中之一 半導體工程師面臨的主要挑戰 然而,在分析他們的解決方案時,圍繞著模擬設計從一個芯片制造工藝節點轉移到另一個芯片制造工藝節點時可以縮小多少。換句話說,某些模擬構建模塊不能充分擴展到較小的IC制造節點。此外,雖然數字邏輯在現代SoC中越來越便宜,但并非所有模擬功能都可以經濟地集成。

“一旦你開始選擇不同的工藝,速度、功耗和成本也成為關鍵的設計考慮因素,”Synopsys物聯網戰略營銷經理Ron Lowman說。雖然一些模擬設計可以利用基于CMOS的標準設計,但較小的物聯網設計確實需要特殊的工藝技術,這成為設計模擬IP的關鍵因素。

圖 1:SoC 設計的模擬/混合信號 IP(左下角)必須符合晶圓廠工藝節點的要求。(來源:新思科技)

在這個十字路口,IP供應商與半導體晶圓廠的密切關系非常重要。以Analog Bits為例,它提供了高性能模擬的基本構建模塊,最近被芯片設計服務提供商SEMIFIVE收購。模擬位加入 英特爾代工服務 (IFS) 以及 2022 年初的 IP 聯盟計劃,以支持英特爾在時鐘、傳感器和 I/O 方面的 16 納米工藝。

Analog Bits還宣布為格芯(GF)的12納米12LP工藝節點提供其IP產品組合,并公布了模擬和混合信號IP的計劃,以滿足 臺積電的 4 納米和 3 納米工藝節點.

模擬 IP 的未來挑戰

雖然從高度手動的模擬設計流程過渡到自動生成模擬IP模塊的代碼可以節省大量時間和集成工作,但這并非沒有挑戰,尤其是當芯片代工廠不斷轉向更小的制造工藝時。

半導體晶圓廠每六個月推出一次新的工藝技術,這些技術不僅僅是前一個節點的縮小版本;它們越來越復雜,并且在結構上與前一個節點不同。這種動態的一個例子是臺積電的新型N3 FINFLEX技術,該技術在鑄造廠的 2022 研討會.

在相當長的一段時間內,向較小節點的過渡一直被視為模擬設計領域的主要絆腳石。這使得IP供應商最近宣布支持4納米和3納米工藝幾何形狀成為一個值得注意的前提。然而,當涉及到主要為數字設計的較小節點時,模擬工程師將不得不以不同的方式做事。

從 鰭式場效應晶體管到全方位柵極 先進節點中的(GAA)制造工藝技術也將帶來獨特的工程挑戰,如電容補償。因此,這些先進節點的模擬集成將需要更高水平的混合信號電路創新。

此外,4 nm和3 nm節點上的模擬和混合信號設計將需要新一代的工具鏈來補充傳統的SPICE模擬器。

“模擬仿真器需要不斷增強其模型解析器,以支持最新和最好的過程節點,”西門子EDA部門AMS部門產品,營銷和業務開發主管Sathish Balasubramanian說。“這一點至關重要,因為模擬模擬器用于表征標準單元庫,這些庫將成為新芯片的基礎數字構建模塊。

圖 2:較小節點上的模擬/混合信號 IP 需要新一代設計工具鏈。(出處:西門子EDA)

此外 EDA 工具鏈,模擬和混合信號IP供應商提供的工具包對于快速跟蹤,簡化和重新風險設計過程也至關重要。這意味著IC開發人員不必弄清楚如何將這些IP構建模塊集成到其SoC設計中。

本文最初發表于 電子電氣時報.

馬吉德·艾哈邁德,EDN和Planet Analog的主編,已經報道了二十多年的電子設計行業。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)