電平觸發的觸發器概述

95

95

拍明

拍明

原標題:電平觸發的觸發器概述

電平觸發的觸發器(Level-Triggered Flip-Flop)是一種基本的數字電路元件,其狀態變化由輸入信號的電平(高電平或低電平)持續時間決定,而非由信號的邊沿(上升沿或下降沿)觸發。與邊沿觸發的觸發器(如D觸發器、JK觸發器)相比,電平觸發觸發器對輸入信號的電平持續時間敏感,適用于需要基于電平狀態進行邏輯控制的場景。

一、電平觸發觸發器的基本原理

工作機制

電平敏感:觸發器的狀態僅在輸入信號處于特定電平(高或低)期間更新。

透明性:在觸發電平有效期間,輸出直接跟隨輸入變化(類似“透明”狀態)。

鎖存特性:當電平無效時,觸發器保持當前狀態,直到下一個有效電平到來。

常見類型

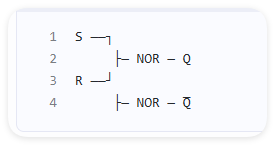

SR鎖存器(Set-Reset Latch):最基本的電平觸發觸發器,由兩個交叉耦合的NOR或NAND門組成。

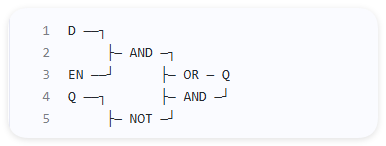

D鎖存器(Data Latch):在SR鎖存器基礎上增加數據輸入端,避免非法狀態(S=R=1)。

Gated鎖存器:通過使能端(Enable)控制電平觸發的有效性(如Gated D鎖存器)。

二、電平觸發觸發器的核心特性

輸入電平持續時間要求

高電平觸發:僅在輸入信號為高電平時,觸發器狀態更新。

低電平觸發:僅在輸入信號為低電平時,觸發器狀態更新。

關鍵點:輸入信號需保持有效電平足夠時間,以確保狀態穩定更新。

透明窗口

在電平有效期間,輸出直接反映輸入(如D鎖存器中Q=D)。

可能導致競爭冒險(Race Condition),需謹慎設計時序。

狀態保持

電平無效時,觸發器保持最后狀態,類似存儲單元。

三、典型電平觸發觸發器結構與真值表

1. SR鎖存器(NOR門實現)

電路結構:

真值表:

| S | R | Q (next) | Q? (next) | 說明 |

|---|---|---|---|---|

| 0 | 0 | Q | Q? | 保持當前狀態 |

| 0 | 1 | 0 | 1 | 復位(Reset) |

| 1 | 0 | 1 | 0 | 置位(Set) |

| 1 | 1 | 非法 | 非法 | 避免同時置位和復位 |

2. D鎖存器

電路結構:

真值表:

EN D Q (next) 說明 0 X Q 保持當前狀態 1 0 0 輸出跟隨輸入(低電平) 1 1 1 輸出跟隨輸入(高電平)

四、電平觸發觸發器的優缺點

優點

簡單易實現:結構簡單,適合低復雜度電路。

透明性:在電平有效期間可直接傳遞數據,適用于數據總線控制。

低功耗:無邊沿檢測電路,靜態功耗較低。

缺點

競爭冒險:輸入信號在電平有效期間變化可能導致輸出不穩定。

時序敏感:需嚴格控制輸入信號的電平持續時間,否則可能丟失數據。

抗干擾能力弱:對毛刺(Glitch)敏感,易誤觸發。

五、電平觸發觸發器的應用場景

數據總線控制

示例:在微處理器中,使用D鎖存器暫存總線數據,確保數據在電平有效期間穩定傳輸。

時序邏輯簡化

示例:在簡單狀態機中,通過電平觸發觸發器實現狀態轉移,減少邊沿檢測邏輯。

低速系統設計

適用場景:對時序要求不嚴格的系統(如低頻控制電路)。

六、電平觸發與邊沿觸發的對比

| 特性 | 電平觸發觸發器 | 邊沿觸發觸發器 |

|---|---|---|

| 觸發條件 | 輸入信號電平(高/低) | 輸入信號的上升沿或下降沿 |

| 透明性 | 是(電平有效期間輸出跟隨輸入) | 否(僅在邊沿瞬間采樣輸入) |

| 抗干擾能力 | 弱(對毛刺敏感) | 強(僅響應邊沿) |

| 典型應用 | 數據總線、低速控制 | 時序邏輯、高速信號處理 |

| 設計復雜度 | 低 | 高(需精確控制邊沿) |

七、電平觸發觸發器的設計注意事項

輸入信號穩定性

確保輸入信號在電平有效期間保持穩定,避免抖動。

電平持續時間

根據觸發器延遲時間,確保輸入信號電平持續時間足夠(通常需大于觸發器建立時間和保持時間之和)。

避免非法狀態

在SR鎖存器中,避免S=R=1;在D鎖存器中,確保使能信號與數據信號同步。

八、總結

電平觸發的觸發器以其簡單性和透明性在低復雜度數字電路中具有重要應用,尤其適合數據總線控制和時序邏輯簡化場景。然而,其時序敏感性和抗干擾能力弱的缺點限制了其在高速或高可靠性系統中的使用。設計時需根據具體需求權衡利弊,合理選擇觸發器類型。

選型建議:

需要透明數據傳遞:選擇D鎖存器。

需要簡單狀態控制:選擇SR鎖存器或Gated鎖存器。

高速或高可靠性場景:優先選擇邊沿觸發觸發器(如D觸發器、JK觸發器)。

四、電平觸發觸發器的優缺點

優點

簡單易實現:結構簡單,適合低復雜度電路。

透明性:在電平有效期間可直接傳遞數據,適用于數據總線控制。

低功耗:無邊沿檢測電路,靜態功耗較低。

缺點

競爭冒險:輸入信號在電平有效期間變化可能導致輸出不穩定。

時序敏感:需嚴格控制輸入信號的電平持續時間,否則可能丟失數據。

抗干擾能力弱:對毛刺(Glitch)敏感,易誤觸發。

五、電平觸發觸發器的應用場景

數據總線控制

示例:在微處理器中,使用D鎖存器暫存總線數據,確保數據在電平有效期間穩定傳輸。

時序邏輯簡化

示例:在簡單狀態機中,通過電平觸發觸發器實現狀態轉移,減少邊沿檢測邏輯。

低速系統設計

適用場景:對時序要求不嚴格的系統(如低頻控制電路)。

六、電平觸發與邊沿觸發的對比

| 特性 | 電平觸發觸發器 | 邊沿觸發觸發器 |

|---|---|---|

| 觸發條件 | 輸入信號電平(高/低) | 輸入信號的上升沿或下降沿 |

| 透明性 | 是(電平有效期間輸出跟隨輸入) | 否(僅在邊沿瞬間采樣輸入) |

| 抗干擾能力 | 弱(對毛刺敏感) | 強(僅響應邊沿) |

| 典型應用 | 數據總線、低速控制 | 時序邏輯、高速信號處理 |

| 設計復雜度 | 低 | 高(需精確控制邊沿) |

七、電平觸發觸發器的設計注意事項

輸入信號穩定性

確保輸入信號在電平有效期間保持穩定,避免抖動。

電平持續時間

根據觸發器延遲時間,確保輸入信號電平持續時間足夠(通常需大于觸發器建立時間和保持時間之和)。

避免非法狀態

在SR鎖存器中,避免S=R=1;在D鎖存器中,確保使能信號與數據信號同步。

八、總結

電平觸發的觸發器以其簡單性和透明性在低復雜度數字電路中具有重要應用,尤其適合數據總線控制和時序邏輯簡化場景。然而,其時序敏感性和抗干擾能力弱的缺點限制了其在高速或高可靠性系統中的使用。設計時需根據具體需求權衡利弊,合理選擇觸發器類型。

選型建議:

需要透明數據傳遞:選擇D鎖存器。

需要簡單狀態控制:選擇SR鎖存器或Gated鎖存器。

高速或高可靠性場景:優先選擇邊沿觸發觸發器(如D觸發器、JK觸發器)。

責任編輯:David

【免責聲明】

1、本文內容、數據、圖表等來源于網絡引用或其他公開資料,版權歸屬原作者、原發表出處。若版權所有方對本文的引用持有異議,請聯系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學習使用,不涉及商業目的。

3、本文內容僅代表作者觀點,拍明芯城不對內容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關結果。

4、如需轉載本方擁有版權的文章,請聯系拍明芯城(marketing@iczoom.com)注明“轉載原因”。未經允許私自轉載拍明芯城將保留追究其法律責任的權利。

拍明芯城擁有對此聲明的最終解釋權。

產品分類

產品分類

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權所有 客服熱線:400-693-8369 (9:00-18:00)