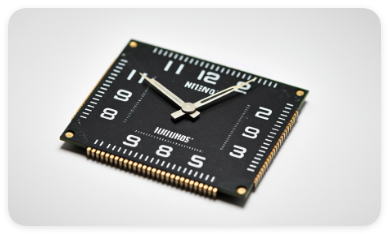

MSP430時鐘輸出的配置方式有哪些?

7

7

拍明芯城

拍明芯城

MSP430單片機的時鐘輸出配置涉及時鐘源選擇、引腳功能分配、分頻系數(shù)設(shè)置等核心步驟,需結(jié)合具體型號的硬件資源(如外設(shè)模塊、可用引腳)和功能需求進行靈活設(shè)計。以下從配置邏輯、寄存器操作、典型場景三個維度展開,無代碼示例或公式,聚焦核心方法與關(guān)鍵細節(jié)。

一、MSP430時鐘輸出的配置核心步驟

MSP430的時鐘輸出配置需完成以下四步操作,按順序執(zhí)行可避免資源沖突或時鐘異常:

1. 確定時鐘源

可選時鐘源:

ACLK:通常由LFXT(32.768kHz晶振)、VLO(內(nèi)部低頻振蕩器)或REFO(參考振蕩器)驅(qū)動。

SMCLK:通常由DCO(數(shù)字控制振蕩器)、HFXT(高頻晶振)或ACLK分頻驅(qū)動。

MCLK:通常由DCO或HFXT驅(qū)動,負責(zé)CPU和核心外設(shè)。

模塊級時鐘:如Timer_A/B的TAxCLK(可接ACLK/SMCLK/外部時鐘)、USCI的通信時鐘等。

選擇依據(jù):

低功耗場景:優(yōu)先使用ACLK(LFXT或VLO驅(qū)動),如驅(qū)動RTC或低速傳感器。

高速外設(shè)場景:使用SMCLK(DCO或HFXT驅(qū)動),如驅(qū)動SPI/I2C或ADC。

實時性需求:MCLK直接輸出CPU頻率,用于調(diào)試或外部高速設(shè)備同步。

2. 配置時鐘分頻系數(shù)

分頻作用:調(diào)整輸出時鐘頻率以匹配外設(shè)需求(如UART波特率、PWM頻率)。

寄存器配置:

ACLK分頻:通過

BCSCTLx寄存器的DIVAx字段(如DIVA_0不分頻,DIVA_1/2分頻)。SMCLK分頻:通過

BCSCTLx寄存器的DIVSx字段(如DIVS_0不分頻,DIVS_3/8分頻)。MCLK分頻:部分型號支持MCLK分頻(如

BCSCTL2.DIVMx),但通常直接輸出CPU頻率。模塊級分頻:如Timer_A的

TACCRx寄存器可配置PWM占空比和頻率,USCI的波特率寄存器可配置通信時鐘分頻。設(shè)計要點:

確保分頻后的時鐘頻率滿足外設(shè)要求(如UART波特率誤差<3%)。

避免分頻系數(shù)為0(可能引發(fā)寄存器配置錯誤)。

3. 分配時鐘輸出引腳

引腳選擇規(guī)則:

固定功能引腳:部分型號的時鐘輸出引腳是固定的(如P1.0輸出ACLK,P2.0輸出SMCLK),需查閱芯片手冊確認。

可復(fù)用引腳:通過

PxSEL或PxSEL2寄存器將GPIO引腳配置為時鐘輸出功能(如P1SEL |= BIT0將P1.0配置為ACLK輸出)。沖突規(guī)避:

同一引腳不可同時配置為GPIO輸入/輸出和時鐘輸出。

動態(tài)切換引腳功能時需先關(guān)閉時鐘輸出,再重新配置寄存器。

4. 啟用時鐘輸出

寄存器使能位:

系統(tǒng)時鐘輸出:通過

BCSCTLx或UCSCTLx寄存器的時鐘輸出使能位(如UCSCTL4.SELAx選擇ACLK源)。模塊級時鐘輸出:通過模塊控制寄存器啟用輸出(如

TAxCTL.OUTMODx配置Timer_A的PWM輸出模式)。啟動延遲:

外部晶振驅(qū)動的時鐘(如ACLK的LFXT)需等待啟動穩(wěn)定(>1ms),否則可能輸出錯誤頻率。

內(nèi)部DCO的時鐘輸出無需等待,但需確保校準值已加載(如

CALDCO_8MHZ)。

二、典型時鐘輸出配置場景

以下場景覆蓋MSP430時鐘輸出的常見需求,直接給出配置邏輯與關(guān)鍵寄存器:

場景1:輸出ACLK(32.768kHz)到P1.0引腳

配置步驟:

選擇ACLK源:

BCSCTL3 |= LFXT1S_2(使用VLO驅(qū)動ACLK,或LFXT1S_0使用LFXT晶振)。配置分頻系數(shù):

BCSCTL1 &= ~DIVA_3(ACLK不分頻,默認32.768kHz)。分配引腳:

P1SEL |= BIT0(將P1.0配置為ACLK輸出功能)。啟用輸出:無需額外使能位(ACLK默認輸出到配置引腳)。

典型應(yīng)用:驅(qū)動外部RTC芯片或低功耗傳感器。

場景2:輸出SMCLK(8MHz)到P2.0引腳

配置步驟:

選擇SMCLK源:

UCSCTL4 |= SELS_5(使用DCO驅(qū)動SMCLK,并加載校準值CALDCO_8MHZ)。配置分頻系數(shù):

BCSCTL2 &= ~DIVS_3(SMCLK不分頻,默認8MHz)。分配引腳:

P2SEL |= BIT0(將P2.0配置為SMCLK輸出功能)。啟用輸出:無需額外使能位(SMCLK默認輸出到配置引腳)。

典型應(yīng)用:驅(qū)動外部SPI閃存或高速ADC。

場景3:輸出Timer_A的PWM信號到P1.1引腳

配置步驟:

頻率:

TA0CCR0 = 1000(周期寄存器,決定PWM頻率)。占空比:

TA0CCR1 = 300(比較寄存器,決定高電平時間)。選擇Timer_A時鐘源:

TA0CTL |= TASSEL_2(使用SMCLK驅(qū)動Timer_A)。配置PWM模式:

TA0CCTL1 |= OUTMOD_7(PWM復(fù)位/置位模式)。設(shè)置頻率與占空比:

分配引腳:

P1SEL |= BIT1(將P1.1配置為Timer_A輸出功能)。啟動定時器:

TA0CTL |= MC_1(增計數(shù)模式)。典型應(yīng)用:驅(qū)動LED調(diào)光或小型直流電機。

場景4:輸出UART波特率時鐘到USCI模塊

配置步驟:

選擇UART時鐘源:

UCA0CTL1 |= UCSSEL_2(使用SMCLK驅(qū)動UART)。配置分頻系數(shù):通過

UCA0BRx和UCA0MCTLx寄存器設(shè)置波特率(如9600bps)。分配引腳:

P1SEL |= BIT1 + BIT2(將P1.1配置為UART TX,P1.2配置為UART RX)。啟用UART:

UCA0CTL1 &= ~UCSWRST(退出復(fù)位狀態(tài))。典型應(yīng)用:與外部設(shè)備(如藍牙模塊)進行串口通信。

三、時鐘輸出配置的注意事項

時鐘源穩(wěn)定性

外部晶振(LFXT/HFXT)需等待啟動穩(wěn)定(>1ms),否則可能輸出錯誤頻率。

內(nèi)部DCO的時鐘輸出受溫度/電壓影響,對精度敏感的場景需啟用FLL或外接晶振。

引腳功能沖突

同一引腳可能同時支持GPIO、時鐘輸出、外設(shè)功能(如UART TX),需通過寄存器明確配置。

動態(tài)切換引腳功能時需先關(guān)閉時鐘輸出,再重新配置寄存器。

功耗與性能權(quán)衡

高頻時鐘輸出(如SMCLK)會顯著增加功耗,需在低功耗模式下關(guān)閉非必要輸出。

動態(tài)調(diào)整時鐘分頻系數(shù)可優(yōu)化功耗(如空閑時降低ADC采樣時鐘頻率)。

EMI與信號完整性

高頻時鐘輸出(如>10MHz)可能引發(fā)電磁干擾(EMI),需通過PCB布局優(yōu)化(如短走線、接地層隔離)或軟件濾波(如展頻時鐘)緩解。

長距離時鐘輸出需考慮信號衰減,必要時增加驅(qū)動緩沖器。

四、總結(jié):MSP430時鐘輸出配置的邏輯框架

MSP430的時鐘輸出配置需遵循“時鐘源→分頻→引腳分配→使能輸出”的順序,核心要點如下:

明確需求:根據(jù)外設(shè)類型(如RTC、SPI、PWM)選擇合適的時鐘源和頻率。

查閱手冊:確認目標型號的時鐘輸出引腳是否可復(fù)用,以及是否需要額外使能位。

分步配置:優(yōu)先配置時鐘源和分頻系數(shù),再分配引腳并啟用輸出。

動態(tài)優(yōu)化:在低功耗模式下關(guān)閉非必要時鐘輸出,通過寄存器動態(tài)調(diào)整頻率。

通過合理配置時鐘輸出,MSP430可實現(xiàn)外設(shè)同步、模塊復(fù)用、系統(tǒng)級調(diào)試等功能,同時兼顧低功耗與實時性需求,尤其適用于物聯(lián)網(wǎng)(IoT)設(shè)備、可穿戴設(shè)備及便攜式傳感器等場景。

責(zé)任編輯:Pan

【免責(zé)聲明】

1、本文內(nèi)容、數(shù)據(jù)、圖表等來源于網(wǎng)絡(luò)引用或其他公開資料,版權(quán)歸屬原作者、原發(fā)表出處。若版權(quán)所有方對本文的引用持有異議,請聯(lián)系拍明芯城(marketing@iczoom.com),本方將及時處理。

2、本文的引用僅供讀者交流學(xué)習(xí)使用,不涉及商業(yè)目的。

3、本文內(nèi)容僅代表作者觀點,拍明芯城不對內(nèi)容的準確性、可靠性或完整性提供明示或暗示的保證。讀者閱讀本文后做出的決定或行為,是基于自主意愿和獨立判斷做出的,請讀者明確相關(guān)結(jié)果。

4、如需轉(zhuǎn)載本方擁有版權(quán)的文章,請聯(lián)系拍明芯城(marketing@iczoom.com)注明“轉(zhuǎn)載原因”。未經(jīng)允許私自轉(zhuǎn)載拍明芯城將保留追究其法律責(zé)任的權(quán)利。

拍明芯城擁有對此聲明的最終解釋權(quán)。

產(chǎn)品分類

產(chǎn)品分類

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版權(quán)所有 客服熱線:400-693-8369 (9:00-18:00)